## SAT-10.326-2-EEEA-05

# **Investigation of Power MOSFET Transistors Characteristics**

Seher Kadirova. Teodor Nenov

# **Изследване на характеристиките на мощни MOSFET транзистори** Сехер Кадирова, Теодор Ненов

**Abstract:** The next generation of power devices must cover the requirements for characteristics demanded by the load, as well as some specific requirements like limited space and high ambient temperature. Usually active power devices operate at higher switching frequencies to shrink the passive components volume. The publication presents a model for investigation of the characteristics of different power MOSFET transistors at same test conditions. A methodology for evaluation of MOSFET characteristics is developed. The switching transient waveforms for a power MOSFET (turn-on), load characteristics and gate threshold voltages, ensuring stable operation of the **p** and **n** channel MOS transistors have been evaluated.

**Key words:** MOSFET transistors; Switching characteristics, Load Characteristics; Gate threshold voltage.

#### INTRODUCTION

Power semiconductor devices have wide applications in telecommunication, military, and aerospace sectors mainly as switches in power electronic systems. A major factor in this relation is the potential for extremely fast switching. The switching performance of the device is determined by the time required for voltage changes across capacitances.

Power MOSFETs are the most commonly used power devices due to their superior performance over BJT, IGBT, thyristor, etc. They need lower gate drive power, and have faster switching time, no secondary breakdown, and stable gain and response time over a wide temperature range [2].

Unlike the bipolar transistor, which is current driven, Power MOSFETs, with their insulated gates, are voltage driven. A basic knowledge of the principles of driving the gates of these devices allows speeding up or slowing down the switching speeds according to the requirements of the application. MOSFET - is an acronym for Metal Oxide Semiconductor Field Effect Transistor and it is the key component in high frequency, high efficiency switching applications across the electronics industry. Nowadays, millions of modern MOSFET transistors are integrated in electronic components. microprocessors, through "discrete" power transistors. The focus of this topic is the gate drive requirements of the power MOSFET in various switch mode power conversion applications [1,3].

The MOSFET transistors are charge controlled devices which means that their output current is proportional to the charge established in the semiconductor by the control electrode. When these devices are used as switches, both must be driven from a low impedance source capable of sourcing and sinking sufficient current to provide for fast insertion and extraction of the controlling charge. Therefore the MOSFETs have to be driven just as "hard" during turn-on and turn-off as a bipolar transistor to achieve comparable switching speeds. Typical values in power devices are approximately 20 to 200 picoseconds depending on the size of the device. The popularity and proliferation of MOSFET technology for digital and power applications is driven by two of their major advantages. One of these benefits is the ease of use of the MOSFET devices in high frequency switching applications. The MOSFET transistors are simpler to drive because their control electrode is isolated from the current conducting silicon, therefore a continuous ON current is not required. Also, the controlling charge and accordingly the storage time in the MOSFET transistors are greatly reduced [3,4].

The aim of the paper is development of a methodology for investigation and evaluation of MOSFET characteristics.

# DEVELOPMENT OF METHODOLOGY FOR EVALUATION OF MOSFET CHARACTERISTICS

Several MOSFET switching characteristic are influenced by the actual value of the gate threshold and Miller plateau voltages. In order to calculate the Miller plateau voltage, one possibility would be to use the gate-to-source threshold voltage ( $V_{TH}$ ) and transconductance of the MOSFET.

## Estimation of U<sub>GS</sub>

$$I_{D1} = K.(V_{GS1} - V_{TH})^2$$

(1)

$$I_{D2} = K.(V_{GS2} - V_{TH})^2$$

(2)

$$V_{TH} = \frac{V_{GS1}.\sqrt{I_{D1}} - V_{GS2}.\sqrt{I_{D2}}}{\left(\sqrt{I_{D2}} - \sqrt{I_{D1}}\right)}$$

(3)

$$K = \frac{I_{D1}}{\left(V_{GS1} - V_{TH}\right)^2} \tag{4}$$

$$V_{GS} = V_{TH} + \sqrt{\frac{I_{LOAD}}{K}}$$

(5)

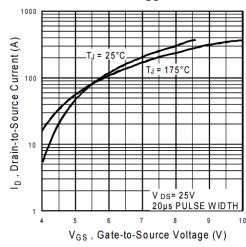

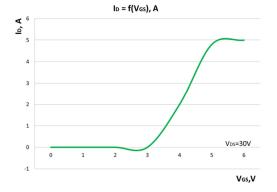

Fig. 1. I<sub>D</sub> - V<sub>GS</sub> relation diagram, temperature curve

The threshold is not very well defined and the listed gfs is a small signal quantity. A more accurate method to obtain the actual  $V_{TH}$  and Miller plateau voltages is to use the Typical Transfer Characteristics curves of the data sheet. From the same temperature curve, pick two easy to read points and note the corresponding drain currents and gate-to-source voltages. Select the drain current values to correspond to vertical grid lines of the graph, that way the currents can be read accurately. Then follow the intersections to the horizontal axes and read the gate-to-source voltages. Starting with the drain currents will result in higher accuracy because the gate-to-source voltage is on a linear scale as opposed to the logarithmic scale in drain current. It is easier to estimate  $V_{GS}1$  and  $V_{GS}2$  on the linear scale therefore the potential errors are much smaller.

# Output characteristics

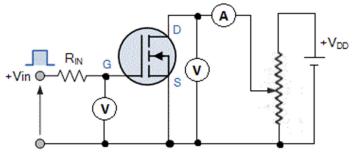

The circuit diagram for determining the drain characteristics with different values of external bias and a family of drain characteristics for different values of gate-source voltage  $V_{\text{GS}}$ .

Fig. 2 Schematic for investigation of the output characteristics

When  $V_{GS}$  is lesser than  $V_{TH}$ ,  $I_D$  is approximately zero. When  $V_{GS}$  is greater than  $V_{TH}$ , the device turns- on and the drain current  $I_D$  is controlled by the gate voltage. At a particular voltage level, which we will shortly define as the threshold voltage, the electron density at the surface exceeds the hole's density. At this voltage, the surface has inverted

# PROCEEDINGS OF UNIVERSITY OF RUSE - 2016, volume 55, book 3.1. НАУЧНИ ТРУДОВЕ НА РУСЕНСКИЯ УНИВЕРСИТЕТ - 2016, том 55, серия 3.1

from the p-type polarity of the original substrate to an n-type inversion layer. This inversion region is an extremely shallow layer, existing as a charge sheet directly below the gate. In the MOS capacitor, the high density of electrons in the inversion layer is supplied by the electron–hole generation process within the depletion layer. The positive charge on the gate is balanced by the combination of negative charge in the inversion layer plus negative ionic acceptor charge in the depletion layer. The voltage at which the surface inversion layer just forms plays an extremely important role in field-effect transistors and is called the threshold voltage  $V_{TH}$ . The region of output characteristics where  $V_{GS}$ < $V_{TH}$  and no current flows, is called the cutt-off region.

#### Transfer characteristics

The transfer characteristic relates drain current ( $I_D$ ) response to the input gate-source driving voltage ( $V_{GS}$ ). Since the gate terminal is electrically isolated from the remaining terminals (drain, source, and bulk), the gate current is essentially zero, so that gate current is not part of device characteristics. The transfer characteristic curve can locate the gate voltage at which the transistor passes current and leaves the OFF-state. This is the device threshold voltage ( $V_{TH}$ ). The transistors are in their non-saturated bias states. As  $V_{GS}$  increases for the nMOS transistor, the threshold voltage is reached where drain current elevates. For  $V_{GS}$ =0V,  $I_D$  is nearly zero indicating that the equivalent resistance between the drain and source terminals is extremely high. Once  $V_{GS}$  reaches 0,7V, the current increases rapidly with  $V_{GS}$  indicating that the equivalent resistance at the drain decreases with increasing gate-source voltage. Therefore, the threshold voltage of the given nMOS transistor is about  $V_{TH} \approx 0.7V$ . The current  $I_{DSS}$  at  $V_{GS}$  <=0 is very small, being of the order of a few nano-amperes.

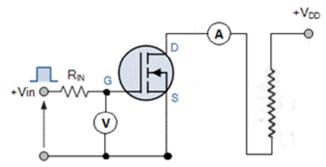

Fig. 3 Schematic for investigation of the Transfer characteristics

## Switching characteristics

When the MOSFET is used as a switch, its basic function is to control the drain current by the gate voltage. The results can be seen on oscilloscope.

#### INVESTIGATION OF POWER MOSFET TRANSISTORS CHARACTERISTICS

The publication presents a methodology for investigation of the characteristics of power MOSFET transistors by experimental stand.

# **RESULTS**

The investigated MOSFET transistor is IRFP 064N.

## • Estimation of UGS

From the temperature curve (fig. 1.), two easy points are picked and noted to the corresponding drain currents and the gate-to-source voltages. The drain current values corresponding to vertical grid lines of the graph are selected. Then the intersections to the horizontal axes have been followed and the gate-to-source voltages are read. The following results have been observed:

At

$$I_{D1} = 11A$$

, the value is  $V_{GS1} = 4,2V$

At

$$I_{D2} = 20A$$

, the value is  $V_{GS2} = 4.5V$

Based on equations 1 and 2 the V<sub>TH</sub> is calculated:

$$I_{D1} = K. (V_{GS1} - V_{TH})^{2}$$

$$I_{D2} = K. (V_{GS2} - V_{TH})^{2}$$

$$V_{TH} = \frac{V_{GS1} \cdot \sqrt{I_{D1}} - V_{GS2} \cdot \sqrt{I_{D2}}}{\left(\sqrt{I_{D2}} - \sqrt{I_{D1}}\right)} = \frac{4, 2.\sqrt{20} - 4, 5.\sqrt{11}}{\left(\sqrt{20} - \sqrt{11}\right)} = 3,327V$$

$$K = \frac{I_{D1}}{\left(V_{GS1} - V_{TH}\right)^2} = \frac{11}{\left(4, 2 - 3,327\right)^2} = 14,211$$

$$V_{GS} = V_{TH} + \sqrt{\frac{I_{LOAD}}{K}} = 3,327 + \sqrt{\frac{1}{14,211}} = 3,39 \text{ V}$$

# Experimental result of measuring the U<sub>GS</sub>

The result observed from the experimental stand is  $U_{GS} = 3,46 \ V$ .

> Estimation of the absolute errors

$$\varepsilon_{abs} = |3,39-3,46| = 0,07V$$

> Estimation of the relative errors

$$\varepsilon_{rell} = \frac{0.07}{3.46}.100 = 2,02\%$$

# Output characteristics

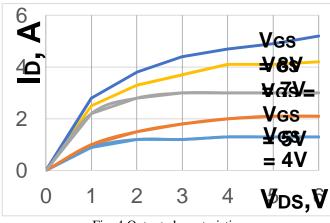

Fig. 4 Output characteristics

The results for drawing diagram are build, using the schematic from fig. 2. The characteristic curves have almost vertical and almost horizontal parts. The almost vertical components of the curves correspond to the ohmic region, and the horizontal components correspond the constant current region. MOSFET can be operated in either of these regions i.e. it can be used as a variable-voltage resistor or as a constant current source.

## Transfer characteristics

The results for drawing the diagram are build, using the schematic from fig. 3. When the  $V_{GS}$  is made positive, the drain current  $I_D$  increases slowly at first, and then much more rapidly with an increase in  $V_{GS}$ .

Fig. 5 Transfer characteristics

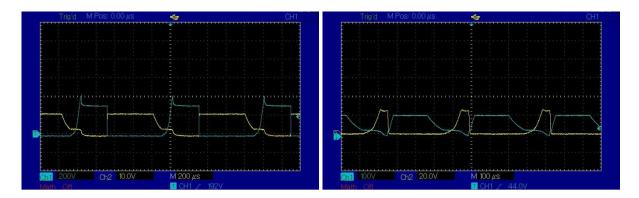

## Switching characteristics

Figure 6 shows a typical switching time test circuit. Also shown are the components of the rise and fall times with reference to the  $V_{GS}$  and  $V_{DS}$  waveforms.

Fig. 6 Results observed from infestation of the switching characteristics

## **CONCLUSIONS AND FUTURE WORK**

An experimental stand for investigation of power MOSFETs characteristics has been developed.

A methodology for evaluation of MOSFET characteristics has been developed. The switching transient waveforms for a power MOSFET (turn-on), load characteristics and gate threshold voltages, ensuring stable operation of the **p** and **n** channel MOS transistors have been evaluated.

The absolute and relative errors of  $U_{GS}$  have been calculated and analysed. The value of relative error is 2,02%, which is the range of acceptable values.

## **REFERENCES**

- [1] Danković D., I. Manić, et al. NBT stress-induced degradation and lifetime estimation in p-channel power VDMOSFETs Microelectron. Reliab., 46 (2006), pp. 1828–1833.

- [2] C.-W. Lee, A. Borne, I. Ferain, A. Afzalian, R. Yan, N. Dehdashti Akhavan, P. Razavi, and J.-P. Colinge, "High-temperature performance of silicon junctionless MOSFETs," Electron Devices, IEEE Transactions on, vol. 57, no. 3, pp. 620 –625, 2010.

- [3] Prerana J., B.K.Mishra, Phade G., 2012, Powergain Analysis of Optically Illuminated MOSFET, International Journal of Computer Application(0975- 8887)-,Vol-51-No.16.

- [4] Stutzke N., B. J. Cheek, S. Kumar, R. J. Baker, A. J. Moll, and W. B. Knowlton, "Effects of Circuit-Level Stress on Inverter Performance and MOSFET Characteristics," in proceedings 2003 IEEE International Integrated Reliability Workshop, 2003, pp. 71-79.

#### **ABOUT THE AUTHORS**

Assistant Prof. Seher Kadirova, PhD, University of Rousse, Department of Electronics, Phone: +359 82 888 516, e-mail: skadirova@ecs.uni-ruse.bg.

Researcher Teodor Nenov, University of Rousse, Department of Electronics Phone:+359 899 401 183; e-mail: tedkata26@mail.bg.